- #Modelsim tutorial video how to

- #Modelsim tutorial video serial

- #Modelsim tutorial video software

- #Modelsim tutorial video code

- #Modelsim tutorial video simulator

The p_CLK_GEN process in the code below creates the 25 MHz clock and will run continuously. Let’s create a signal called r_CLOCK that will have a 25 MHz clock. The first input we should consider is the i_clock input.

#Modelsim tutorial video simulator

We will monitor that signal on the simulator to see if it is responding correctly to changes in input. The one output (w_LED_DRIVE) will not be stimulated. The signals that will need to be stimulated are all of the inputs. If we stimulate the signals on the right, our LED Blinker design will react. Or if you prefer, the signals to the left are the signals in our design, the signals to the right are the signals in our testbench. The signals to the left are the source signals, the signals to the right are the destination signals. You will notice that the => arrow is facing to the right. It serves an additional purpose: it creates a mapping of signals. The instantiation is the piece of code that actually creates the design that we are testing. The actual use of the tutorial_led_blink entity comes when the entity is instantiated, which happens after the "begin" keyword. That tells the simulator that somewhere later in the file we will be using this entity. Here is the component for our design entity: It looks very similar to the entity that it matches. "Component" is a keyword in VHDL that defines for the tools the nature of an entity somewhere in the design. We have not yet discussed what a component is, so now is as good of a time as any. Next is the architecture, signal declaration, and component declaration section. So the entity name implies that this is a testbench for the entity tutorial_led_blink, which is the name of our design we are testing. As a side note, _tb is a notation for testbench.

All of the signals are generated internally to the testbench.

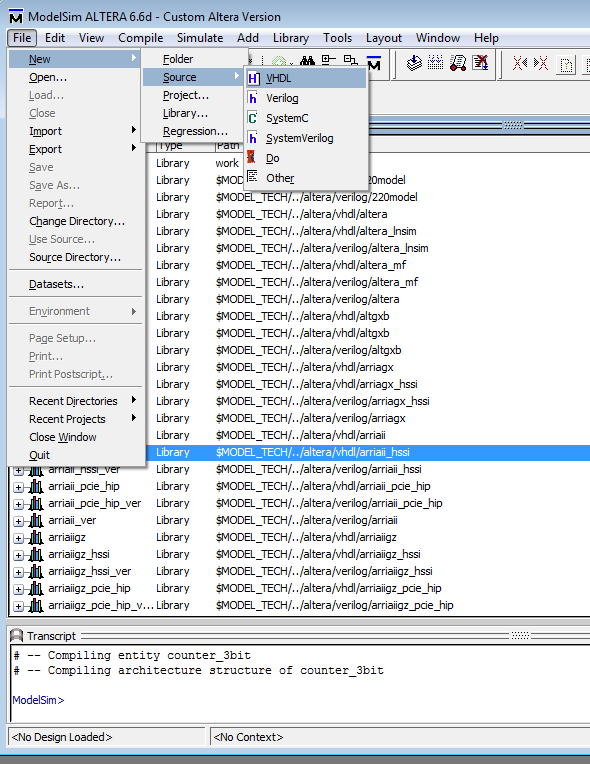

For a testbench, often there will be no input or output signals. As a reminder, the entity contains all of the input signals and output signals. The first thing we need to do is to define the entity of the testbench. There are two sections below, the first shows the VHDL Example, the second shows the Verilog Example. Let’s get started with our first testbench. If the output signal behaves the way you would expect, the test is a success. The testbench will allow us to toggle these switches and observe what happens to the output signal. The testbench allows us to pretend that we have real switches connected to our design. In the LED Blinker code, we expect that the LED should light up at a different frequency based on the switch selections. A testbench is code that exercises a design by observing the outputs of the design when the inputs are stimulated. In order to simulate the design created previously, you need to create what is called a testbench.

#Modelsim tutorial video how to

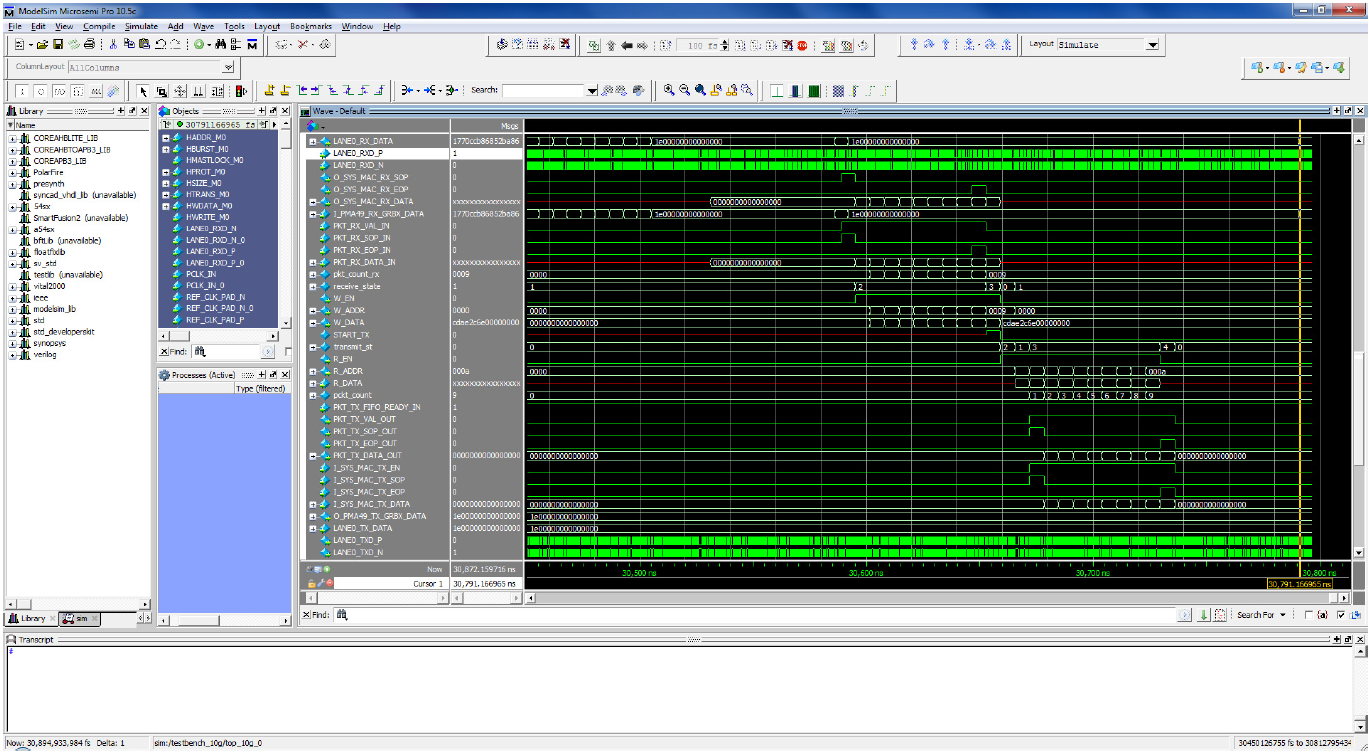

If you've never used Modelsim before, you can learn about how to use it by reading this Modelsim Tutorial for Beginners. Mentor graphics has a student version available. The simulator that is most popular in the commercial world is called Modelsim and it is made by Mentor Graphics. It is very important to check that the code you wrote is behaving the way you expect it to behave. Simulation is a critical part of any design. In this way, the design will be loaded on FGPA board.Tutorial: Your FPGA Program: An LED Blinker Part 2: Simulation of VHDL/Verilog Then click on ‘add file’ and select the ‘.sof/.pof’ file and click on ‘start’.

#Modelsim tutorial video serial

It will show all the input and output ports of the design and we need to fill ‘location’ column for these ports.

#Modelsim tutorial video software

Quartus software generates two types of files after compilation i.e.

0 kommentar(er)

0 kommentar(er)